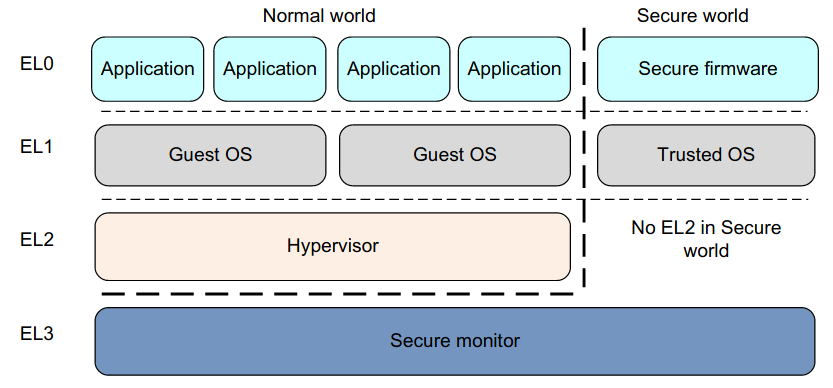

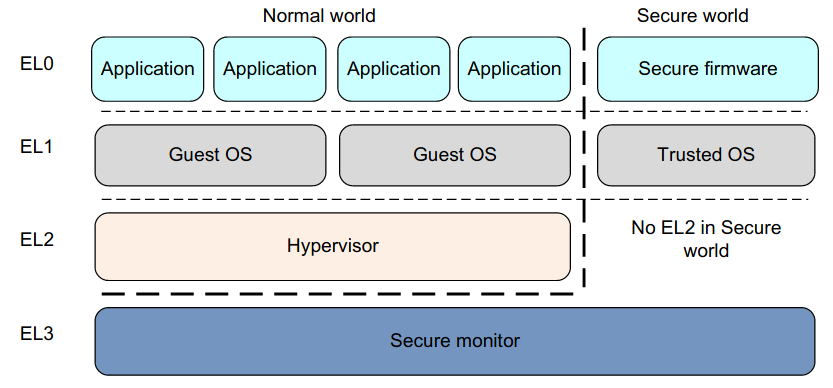

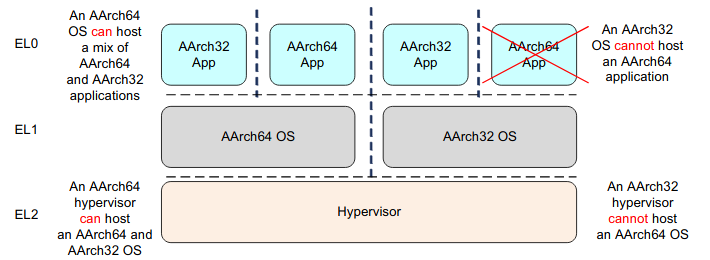

Summary: Exception level / Execution states

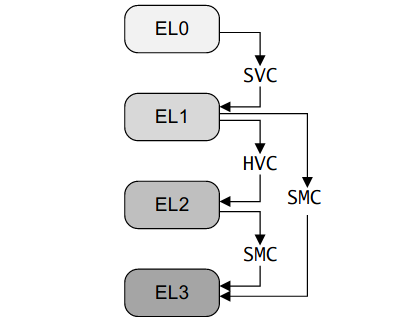

- A logical separation of software execution privilege

- Similar to hierarchical protection domains (e.g., ring in x86)

Taesoo Kim

Taesoo Kim

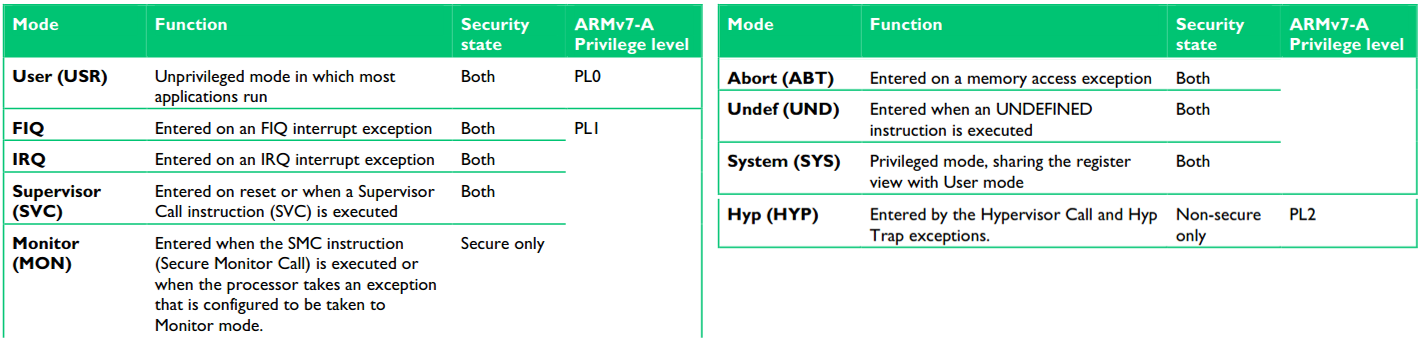

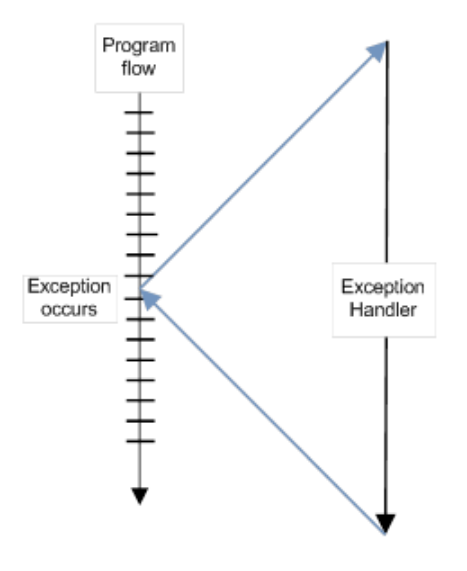

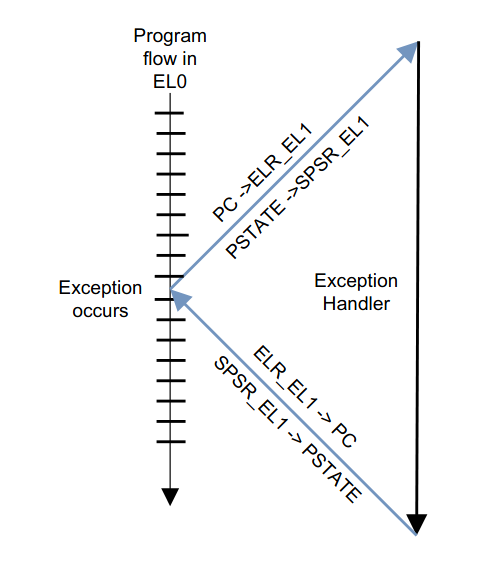

What happens when the processor doesn’t know how to handle the exception?

Are Synchronous Interrupts possible, or are they all asynchronous?

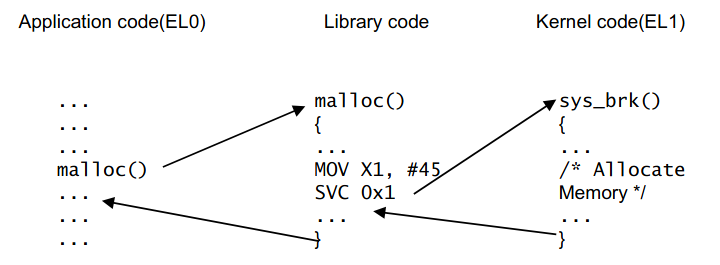

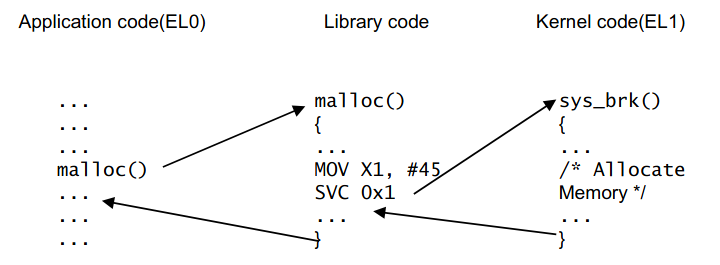

svc (system call), data abort (access violation), etc.

svc), hypervisor call (hvc)-> Interrupt in x86: a control transfer mechanism

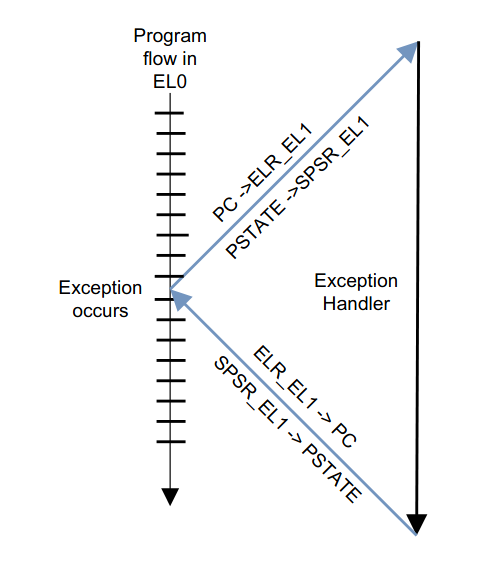

eret (lowering the exception level):

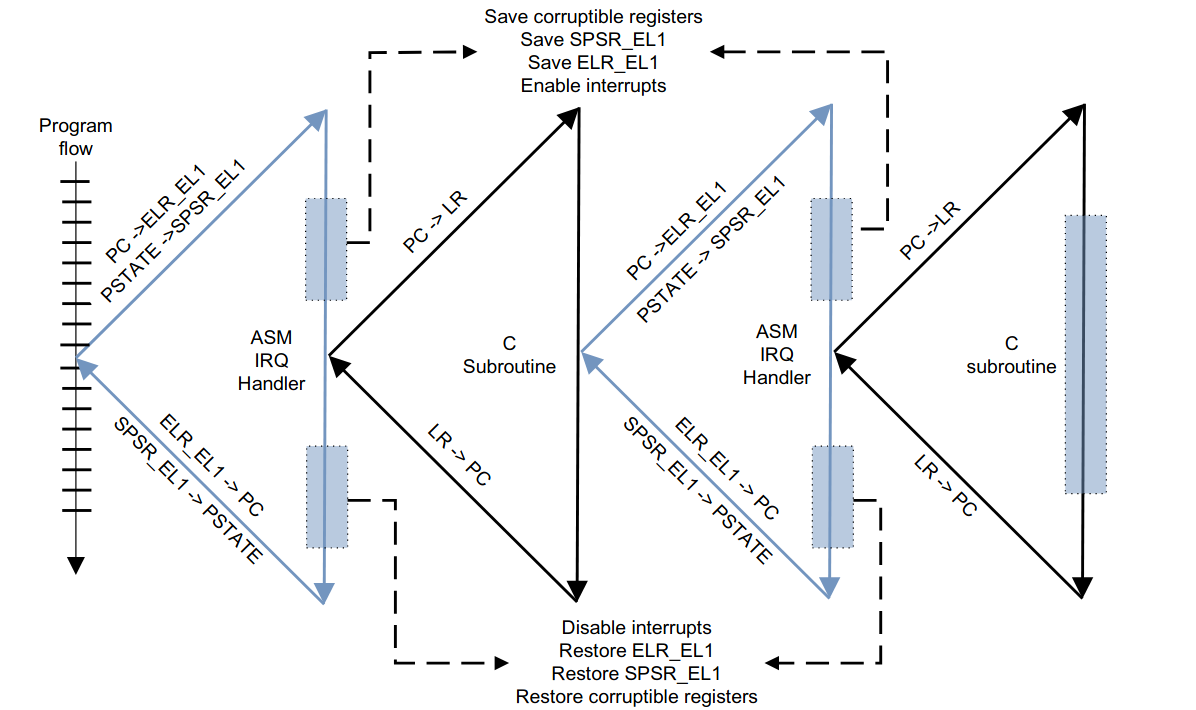

#[no_mangle]

pub extern "C" fn handle_exception( ... ) {

match info.kind {

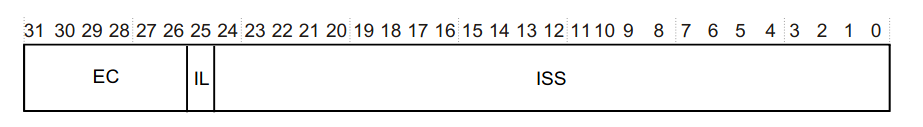

Kind::Synchronous => {

let syndrome = Syndrome::from(esr);

match syndrome {

Syndrome::Brk(_) => { ... }

Syndrome::Svc(n) => { ... }

}

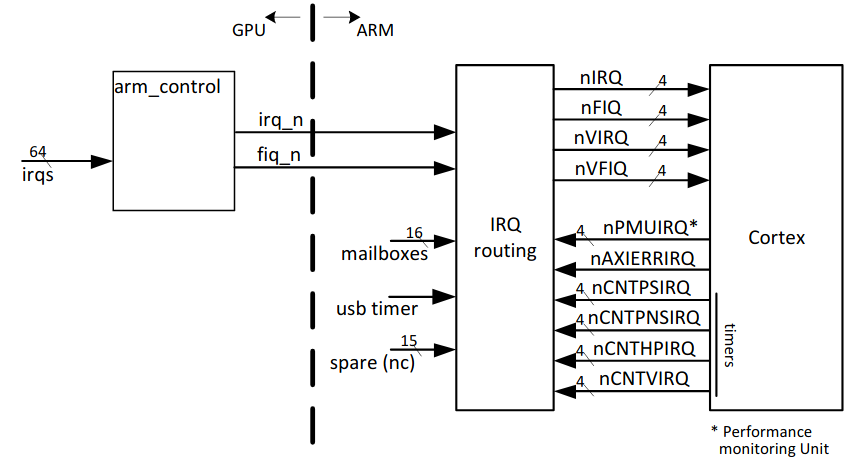

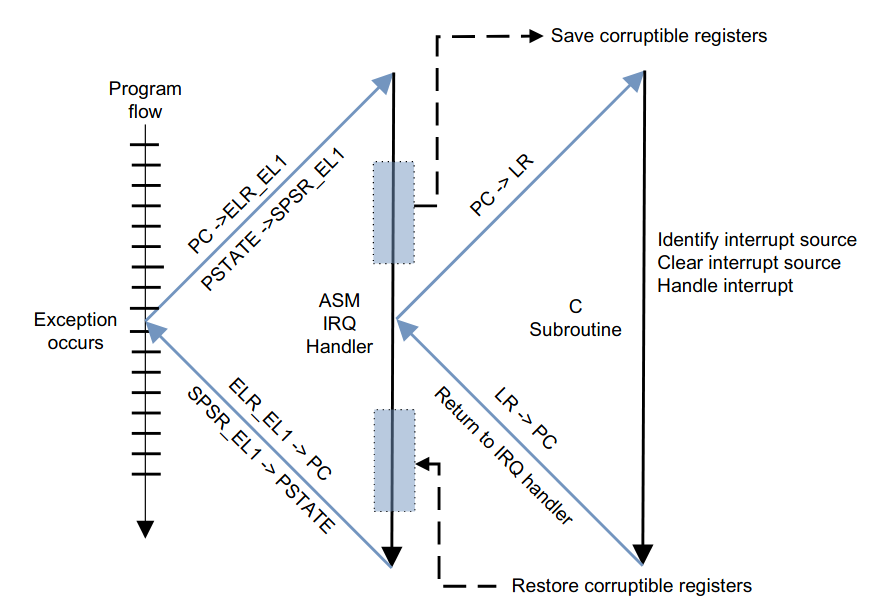

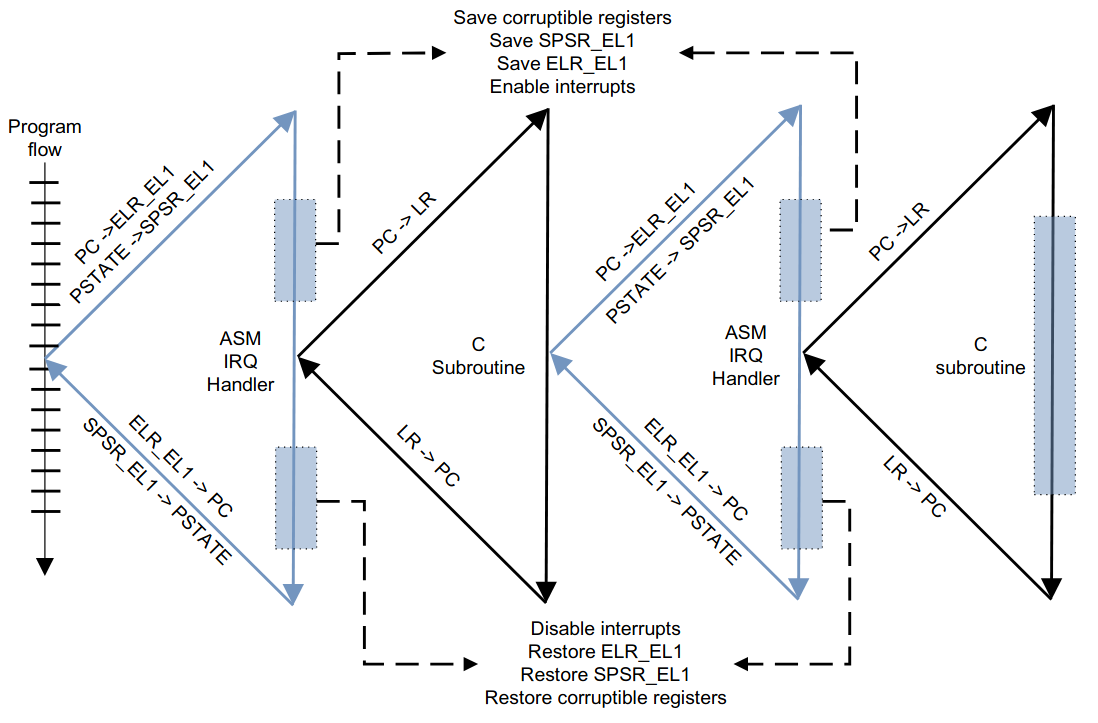

Kind::Irq => {

let ic = Controller::new();

for v in Interrupt::iter() {

if ic.is_pending(v) {

crate::IRQ.invoke(v, tf);

}

}

}

...

}